HDMI1.4协议总结(一):综述和编码方式

综述

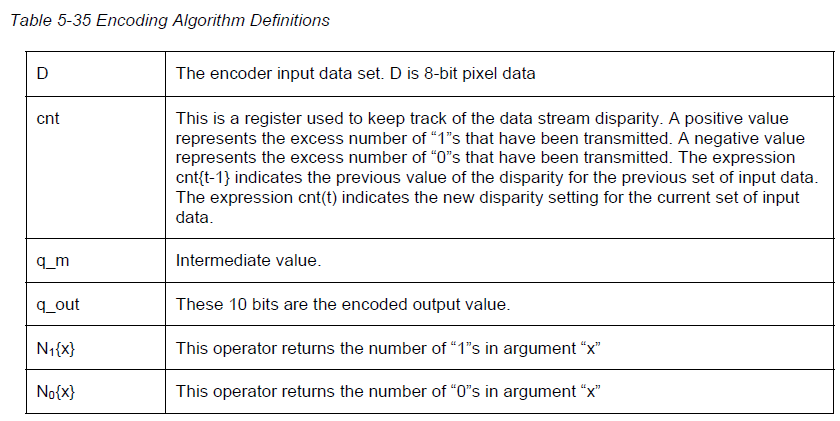

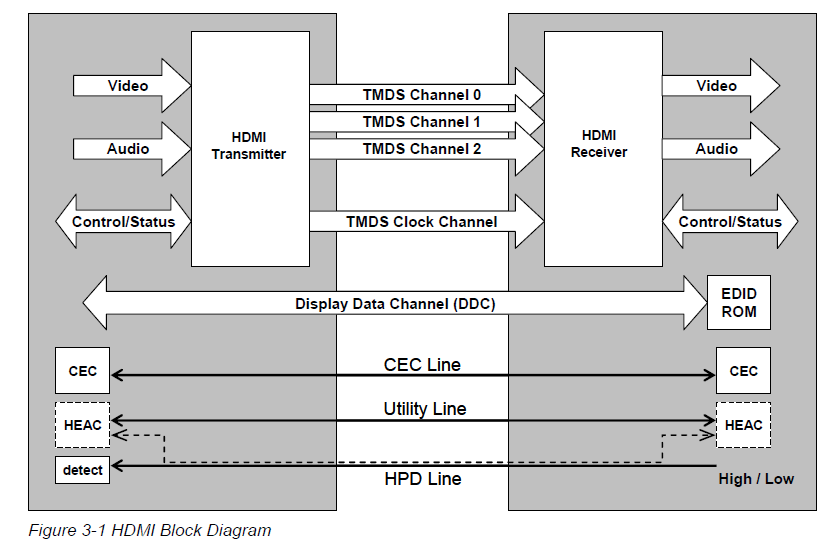

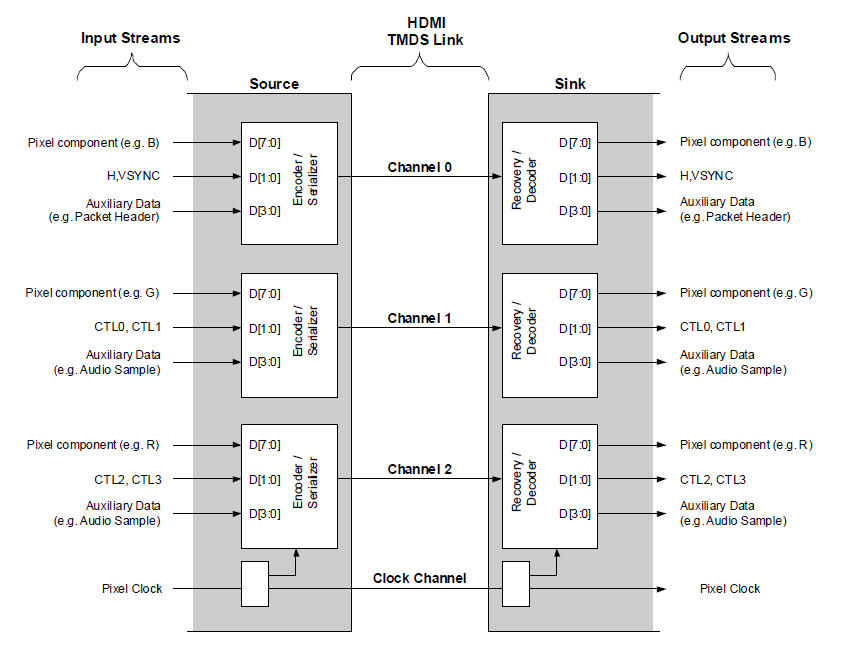

一个HDMI传输系统包括发送端(source)和接收端(sink)。如下图所示,HDMI线缆包括以下连接:

- 由四个差分对组成的主数据通路,包括三个数据通道和一个时钟通道。

- VESA DDC,实际上就是一个I2C bus,用于配置和状态信息的传输

- CEC(optional),消费电子控制

- HEAC,家庭影院系统中音频回传功能

- HPD,热插拔检测

HDMI物理层的实现不在此次赘述,下面直接进入HDMI的数据链路层。

HDMI信号编码

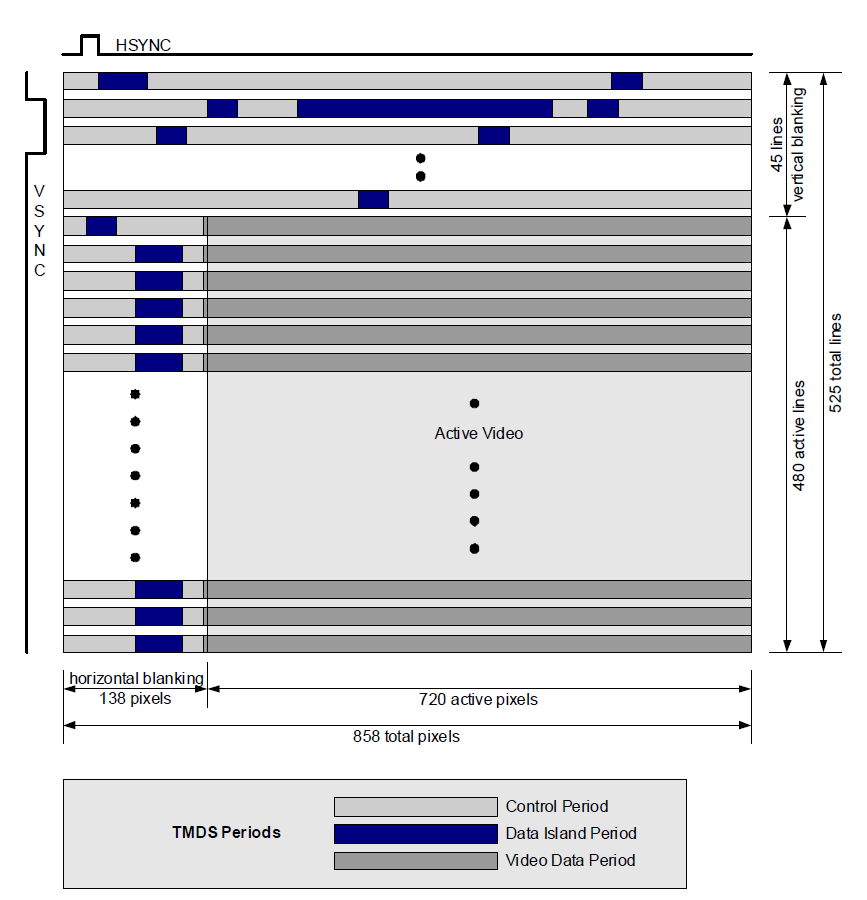

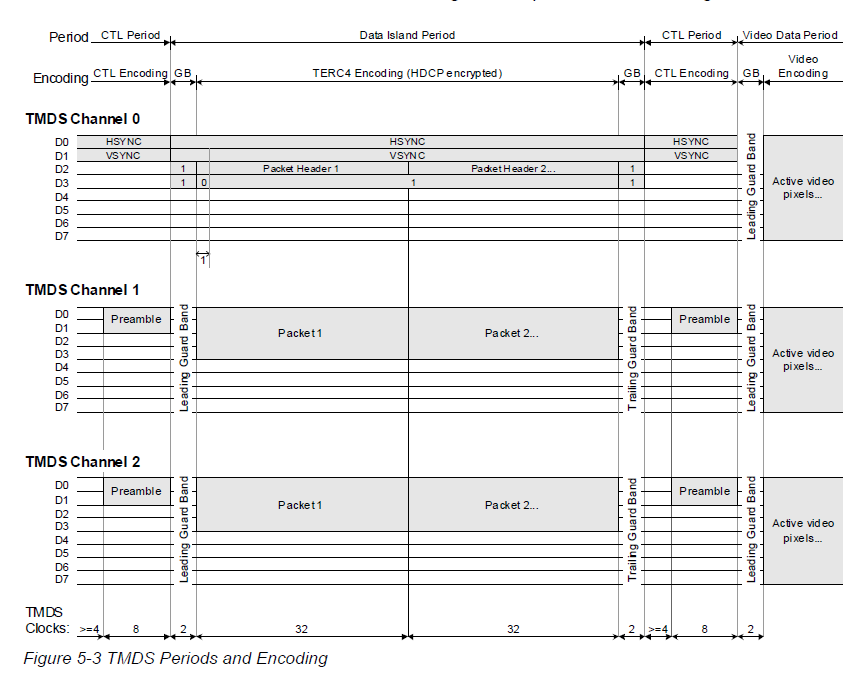

HDMI一共有三种传输模式:Control Period传输control data;Data Island Period传输packet data;Video Data Period传输video data。一个HDMI传输帧的例子如下

同步信号HSYNC和VSYNC会在特定的行、列位置拉起,用于source和sink之间的同步。可以看到实际传输的帧大小是要大于视频大小(720*480p),包括额外插入了一些行,并且行的长度也得到了扩展,这些扩展的区域被称为blank区(包括Vblank和Hblank),blank区由Control Period和Data Island Period交替填充,其中在Data Island Period会传输音频数据和其他辅助数据(例如像素格式等)。实际传输Video Data Period的区域称为active区,传输我们最终会在显示器上看到的视频图像数据。

在HDMI clock channel上每一拍时钟(又称为一个TMDS Clock),每个data channel上都会传输10bit的character。这10bit的character,对于不同的数据,由不同的编码方式得到。control data:2 bit -> 10 bit编码;packet data:4 bit -> 10 bit编码(TERC4编码);video data:8 bit -> 10 bit编码(TMDS编码)。换句话来说,每个TMDS Clock,在每个data channel上,会传输2bit的control data,或者4bit的packet data,或者10bit的control data。这三种数据在data channel上的传输如下图

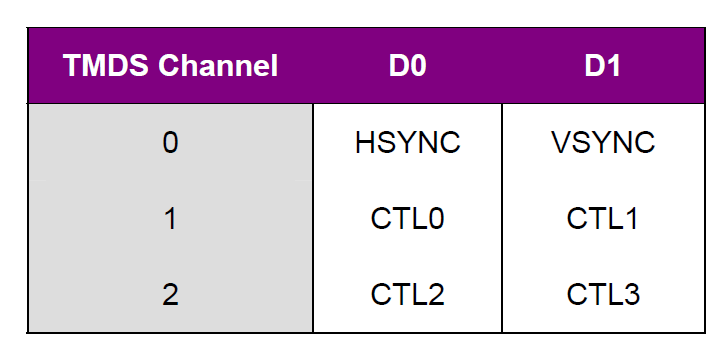

Control data:在channel 0的2bit数据代表HSYNC和VSYNC,channel 1和channel 2上的4bit数据组合构成CTL0-3,其代表的具体信息在后文介绍。

Packet data:channel 0上的4bit数据,由HSYNC、VSYNC以及packet header(这里感觉官方文档给的上面这个示意图不太好,并没有表示其中也包含了HSYNC和VSYNC信息),packet header用于sink判断当前packet的类型(音频包、辅助信息包等);channel 1和channel 2上传输实际packet信息,如音频包会在这两个channel上传输音频信号采样值。

Video data:channel 0到channel 2上总共24bit,均为视频像素数据。

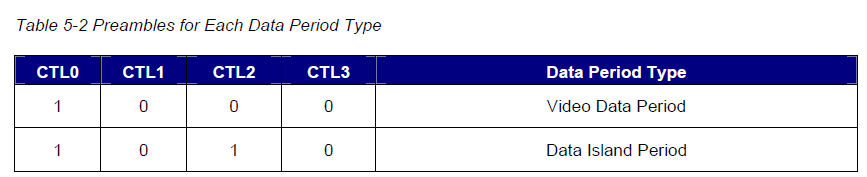

Data Island Period和Video Data Period的传输均需要遵循一定的规则,使得sink端可以正确识别Packet data和Video Data。其传输时序如下:

Data Island Period:

- 紧贴Data Island Period传输的前后,分别有一个Data Island Guard Band(称为Leading Guard Band和Trailing Guard Band),长度均为2个TMDS Clock。

- 在Leading Data Island Guard Band前面,有一个Data Island Preamble,长度为8个TMDS Clock。

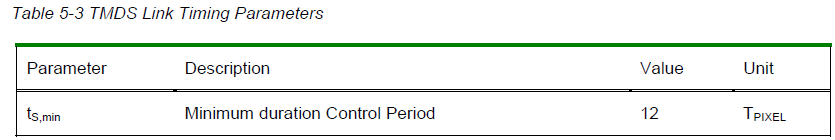

- 由于HDMI1.4 协议规定,每次发Control Period必须连续发至少12个TMDS Clock。由于Data Island Preamble被视为一种特殊的Control Period,因此在Data Island Preamble前面会有至少连续4 TMDS Clock的Control Period。

- 在两个Data Island Guard Band包围起来的中间区域,会发送实际的packet data。每一个packet需要32个TMDS Clock,可以连续发送最少1个,最多18个packet。因此每一个Data Island Period的最小长度为1*32+2*2=36 TMDS Clock(头尾的两个Guard Band也是Data Island Period的一部分)

Video Data Period:

- 与Data Island Period类似,有一个长度为2TMDS Clock的Video Data Guard Band,但仅存在与Video Data Period传输最开始(也即只有Leading Guard Band)。

- 同样有一个长度为8 TMDS Clock的Video Data Preamble。

- Video Data Preamble前面同样会有至少连续4 TMDS Clock的Control Period。

- Data Island Period和Video Data Period不能紧贴,无论哪一个在前,在前者传输完成后必须传输一段Control Period,才能传输后者。

Control Period

Control Period Signal

Control Period在channel 0上传输HSYNC和VSYNC,在channel 1-2上传输CTL0-3。HDMI1.4协议下,CTL0-3主要用于Video Data Preamble和Data Island Preamble传输,以及被sink用作为Character Synchronization(也用于HDCP1.4 EESS信号传输,将在HDCP的文章中介绍)。

Preamble

Channel 0上的HSYNC和VSYNC在Preamble期间按实际情况正常传输

Character Synchronization

注:TMDS Character是指每次编码后,每个TMDS Clock传输的10 bit值。

经过编码后,Video Data Period和Data Island Period的每个character会包含5次或者更少的1->0或0->1跳转,而Control Period会包含7次或更多的跳转。基于此,正如上文一提到的要求,source端的每次Control Period需要持续12个TMDS Clocks,而sink端的解码器应该能识别到这样连续的Contral Period传输,从而同步到Character边界。Sink端的检测算法实现由其自行决定,不在HDMI1.4协议中做要求

每隔一定时间间隔(至少50毫秒一次),source端还被要求要发一个持续时间更长(32 TMDS Clocks)的Control Period,被称为Extended Control Period.

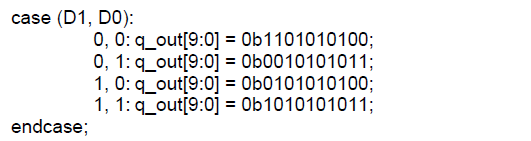

Control Period Encoding

Data Island Period

Data Island Signal

对于Data Island Period(包括对应的Guard Band)的传输,channel 0中的D0和D1分别传输HSYNC 和VSYNC,D2传输Packet Header(在Guard Band区域固定传输1),D3在Leading Guard Band后的第一个TMDS Clock传输0,在其他TMDS Clock(包括Guard Band)传输1(见上面Figure5-3)。channel 1和channel2的总计8bit用于传输Packet Data(Guard Band区域会传输固定的10 bits character)。

Data Island Guard Band

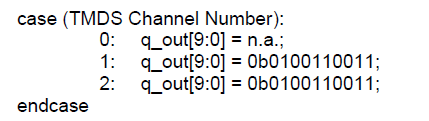

Data Island Guard Band时,channel 1和channel 2被直接编码为实际HDMI Lane上固定的10 bit Character,如下:

channel 0上,基于上文,D2和D3被固定为1,因此,依据HSYNC和VSYNC的取值,channel 0上D[3:0]可能的取值为0xC,0xD,0xE,0xF。channel 0上的D[3:0]通过TERC4编码为10bit character。

Data Island Packet

Packet 结构

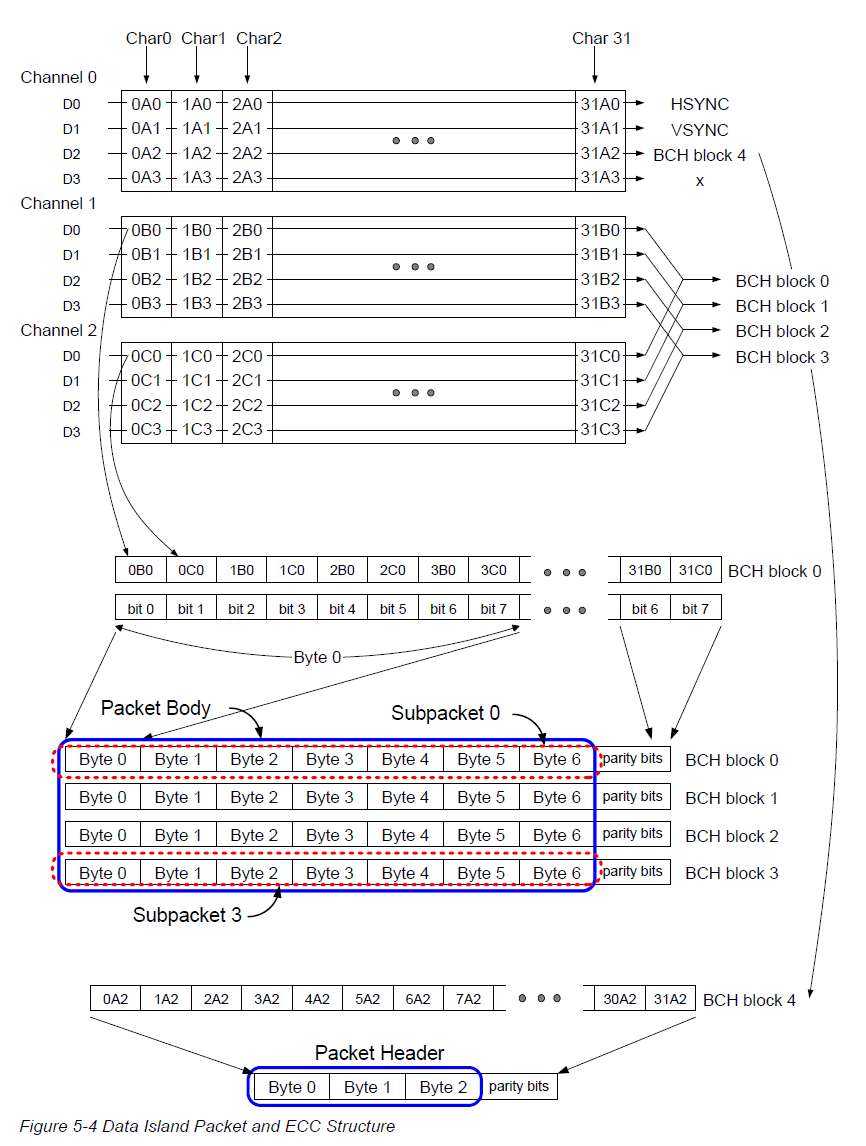

每一个Packet需要32个TMDS Clocks传输,由Packet Header和Packet Body(包含4个Subpackets),以及相应的纠错位(error correction bits)组成。每一个Subpacket包含56bits,并由一个8bits的BCH ECC奇偶校验位(parity bits)保护。

Subpacket 0加上其对应的校验位组成BCH Block 0,其他的BCH Block 1-3也是类似的;BCH Block0-3经过映射之后在channel 1和channel 2上传输。24 bits的Packet Header加上对应的8 bits校验位构成BCH Block4,经过映射后在channel 0的D2上传输。这些传输映射关系如下图所示:

Packet Header的24bits又分为3个Header Bytes:HB0,HB1,HB2。每一个Subpacket的56bits又分为7个Subpacket Bytes:SB0,SB1,……,SB6。

Subpacket0上的SB0-SB6,对应地映射为Packet Bytes,PB0-PB6。以此类推,Subpacket1,2,3上的SB0-SB6,分别映射为PB7-PB13,PB14-PB20,PB21-PB27。

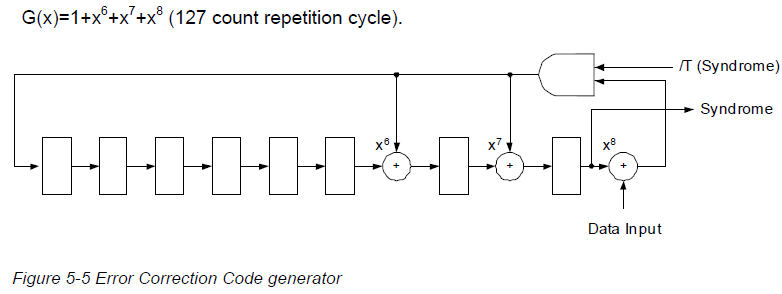

纠错位计算

纠错位计算采用BCH(64,56)和BCH(32,24),纠错位生成器使用的多项式和框图如下所示,具体BCH的原理和计算不在此处赘述。

Packet Header和Packet Body的定义

详见后续HDMI1.4协议系列文章。

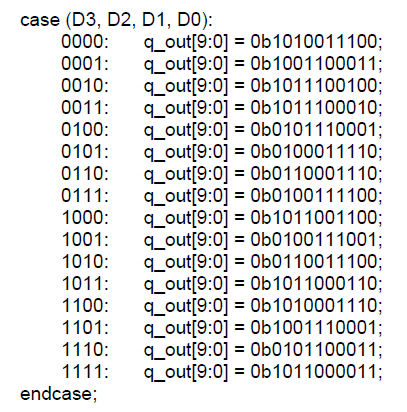

Data Island Period 编码:TERC4

Video Data Period

Video Data Period Signal

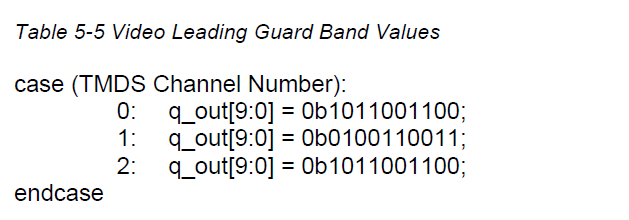

对于Video Data Period的传输,Guard Band时三个channel上都会传输固定的10 bits character,而在active区域传输视频像素时,3个channel上的D[7:0]都传输了8bits的像素数据。

Video Data Guard Band

Pixel Data

详见后续HDMI1.4协议系列文章。

Video Data Period编码:TMDS

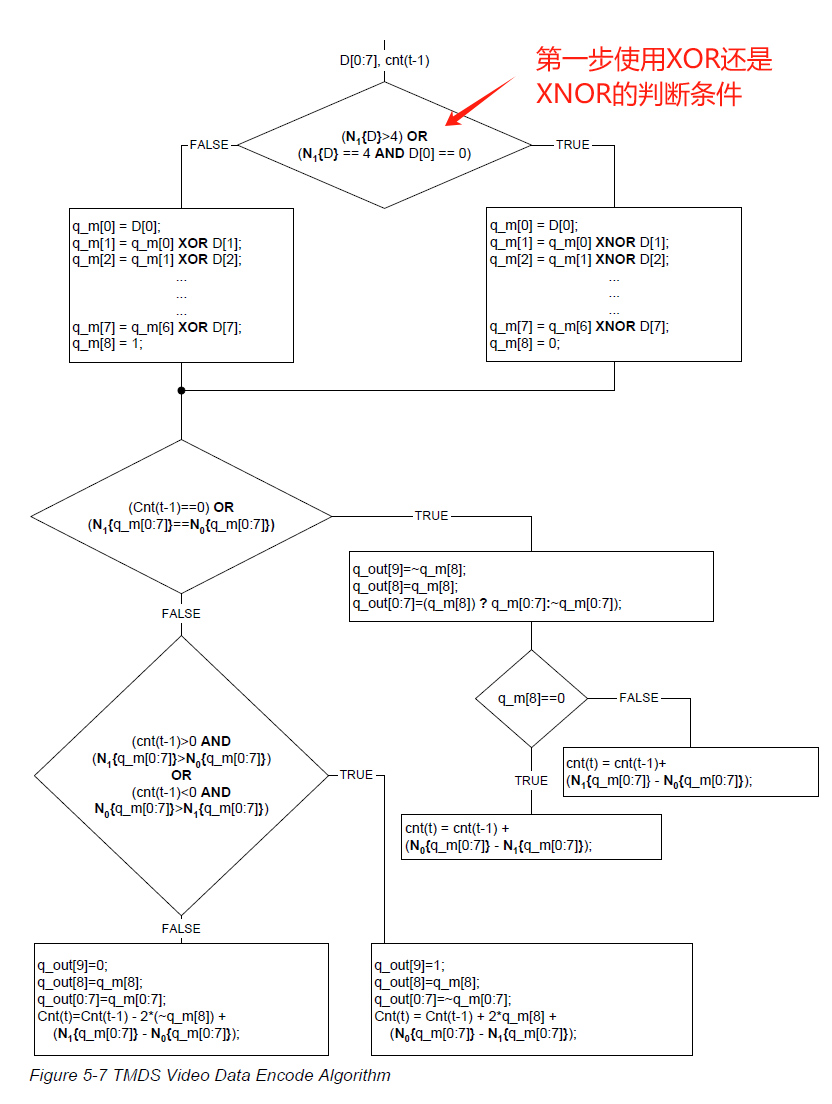

每个channel上的8bits Video Data会被编码为10 bits character,编码原则是实现尽可能的直流平衡(1和0的数量差距尽可能小),以及尽可能减小1和0之间的跳变。编码流程包括两步:第一步是对8bits编码得到最小化跳变的9bits,第二步是将9bits编码为直流平衡的10bits character。

第一步8->9bits的编码:9bits code的LSb等于输入的8bits的LSB,随后的7bit,每一bit的计算都基于如下公式: output[n] = input[n] OR output[n-1],或output[n] = input[n] NOR output[n-1]。具体计算选择XOR(异或)还是XNOR(同或),取决于哪种模式编码得到的9bits code中的跳变更少(算法使用的判断条件如下流程图所示)。9bits code的MSb用于指示当前编码使用的是OR还是NOR。

第二步9->10bits的编码:实现数据流的直流平衡。添加一个第10bit的最高位,以指示是否对数据进行按位取反。编码器基于目前已传输的数据流中0和1的数量差异,以及当前character已编码的低8bits的0和1的数量差异,决定是否进行取反。

所有的编码流程如下图所示。整个编码会产生460种不同的10 bits characters。在编码器正确工作的情况下,不应在Video Data Period产生其他的characters。